The parity generator is a digital combinational circuit, which takes the input data and generates a parity bit depending upon the data. It is generally used in digital transmitters.

Parity generators are classified into:

- Even Parity Generator

- Odd Parity Generator

Tutorials for how to use HDL programming and Simulation tools.

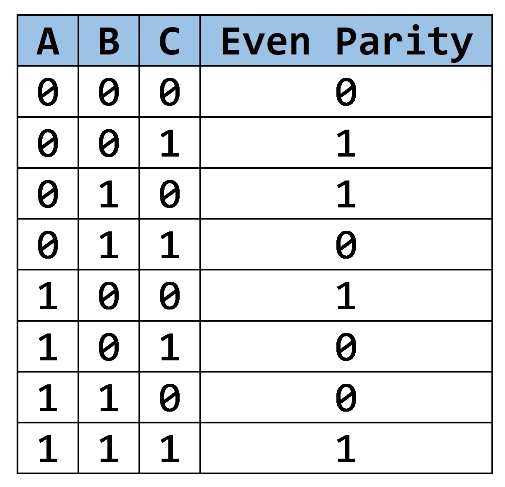

Even Parity Generator

The even parity generator ensures that even number of 1’s is maintained in the output binary data. The output binary data contains all the input bits followed by an extra parity bit. For example, input data is 000, the parity bit will be ‘0’ and if input data is 100, the parity bit will be ‘1’. Thus, maintaining even number of 1’s in binary data.

Truth Table for Even Parity Generator

Programs:

Designmodule even_parity(data_in, parity_out); parameter WIDTH = 3; input [WIDTH-1:0] data_in; output parity_out; assign parity_out = ^data_in; endmodule

Testbenchmodule tb_parity_gen; parameter WIDTH = 4; reg [WIDTH-1:0] data_in; wire parity_out; integer i; even_parity #(.WIDTH(WIDTH)) dut(data_in, parity_out); initial begin for(i = 0; i < 2**WIDTH; i = i + 1) begin data_in = i; #10; end $finish; end endmodule

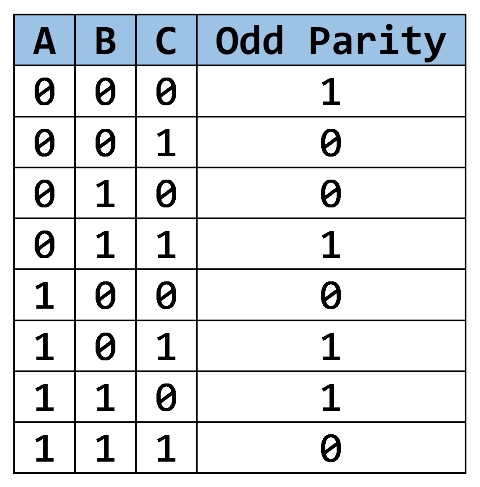

Odd Parity Generator

The odd parity generator ensures that odd number of 1’s is maintained in the output binary data. The output binary data contains all the input bits followed by an extra parity bit. For example, input data is 000, the parity bit will be ‘1’ and if input data is 100, the parity bit will be ‘0’. Thus, maintaining odd number of 1’s in binary data.

Truth Table for Odd Parity Generator

Programs:

Designmodule odd_parity(data_in, parity_out); parameter WIDTH = 3; input [WIDTH-1:0] data_in; output parity_out; assign parity_out = ~^data_in; endmodule

Testbenchmodule tb_parity_gen; parameter WIDTH = 4; reg [WIDTH-1:0] data_in; wire parity_out; integer i; odd_parity #(.WIDTH(WIDTH)) dut(data_in, parity_out); initial begin for(i = 0; i < 2**WIDTH; i = i + 1) begin data_in = i; #10; end $finish; end endmodule

POPULAR TAGS

Travel New York London IKEA NORWAY DIY Ideas Baby Family News Clothing Shopping Sports Games