History

Verilog HDL originated in 1983 at Gateway Design Automation.

The Verilog HDL is now maintained by a non-profit making organisation, Accellera, which was formed from the merger of Open Verilog International (OVI) and VHDL International. OVI had the task of taking the language through the IEEE standardisation procedure.

Today, Verilog HDL is an accepted IEEE standard. In 1995, the original standard IEEE 1364-1995 was approved. IEEE 1364-2001 is the latest Verilog HDL standard that made significant improvements to the original standard.

Mealy FSM with sequence overlap

Program:

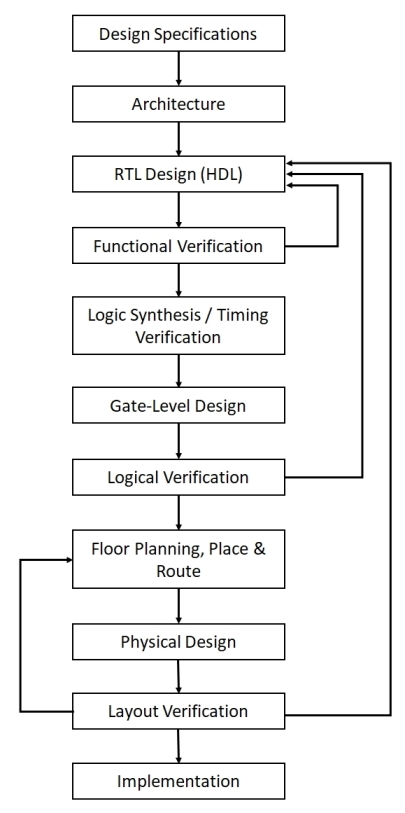

Typical Design Flow

Design Styles

There are two basic design styles in verilog, namely - Top-Down Approach and Bottom-Up Approach.

Top-Down Approach: In top-down approach, we first design a top module and then define the sun-modules in it. Further, we identify the sub-blocks in each sub-module.

Bottom-Up Approach: In bottom-up approach, we first design smaller block and then combine these smaller blocks to build a bigger block. Further, these blocks are combined to finally get a top module.

POPULAR TAGS

Travel New York London IKEA NORWAY DIY Ideas Baby Family News Clothing Shopping Sports Games